# A Design of a High-Performance Analog Front-End for Passive UHF RFID Tag EPC C1G2

Smail Hassouni, and Hassan Qjidaa

Abstract—This paper introduces a high-performance analog front end for passive UHF RFID tag compatible with the EPC Class-1 Generation 2 (EPC C1G2) standard protocol. The proposed front end of a passive tag which contains the following modules: a power generation circuit which is composed of a matching circuit and an RF-limiter circuit, an NMOS rectifier, a DC limiter, a voltage regulation, a modulation and ASK demodulation circuit, a power-on-reset circuit, a ring oscillator which generates a clock of 1.28 MHz. The originality of this work is the proposal of a voltage regulation circuit composed of two distinct LDO regulators that share the same reference voltage and are designed to generate a Vdd1 (0.5 V) for the analog supply and Vdd2 (1 V) for digital power supply, under conditions of 50  $\Omega$  antenna, 900 MHz, a sensitivity of -24 dBm and a maximum consumption of 1 µW. The operating distance of the RFID is more than 25 meters based on the regulated 4 W effective isotropic radiated power (EIRP). The chip area of the proposed analog front end is only 79 µm × 83 µm. The simulation results in 90 nm CMOS process confirm the performance of the proposed analog front-end.

*Index Terms*—Radio frequency identification (RFID), frontend, ultra-high frequency (UHF), RFID Tag, regulator, clock.

## I. INTRODUCTION

The ultra-high frequency (UHF) passive radio frequency identification (RFID) tags are showing a wide range of prospective applications due to their advantages of low cost, long operating distance, high data rate, and small antenna size [1].

The passive RFID tags working at frequencies between 860 MHz to 960 MHz, and 2.4 GHz are suitable for long distance identification. Long distance identification is important in warehouse monitoring, supply-chain management, logistics, and many other areas [2], [3].

The RFID tags are classified into three types of RFID tags, especially passive [4], [5], semi-passive [6], or active.

Manuscript received February 18, 2017; revised April 10, 2018. Date of publication May 25, 2018. Prof. Zoran Blažević has been coordinating the review of this manuscript and approved it for publication.

Authors are with the CED-ST, LESSI, Faculty of sciences Dhar El Mehraz, UniversitySidi Mohamed Ben Abdellah, BP 1796 Fez-Atlas 30030, Fez, Morocco.

E-mails: smail.hassouni@usmba.ac.ma, hassan.qjidaa@usmba.ac.ma. Digital Object Identifier (DOI): 10.24138/jcomss.v14i2.464 The active RFID tags are used in some applications due to their higher communication range and their simpler structure where there is no need to extract power from the input signal.

Today the majority of RFID tags is passive; occupy a major part of the market because they do not need battery where the power is extracted from the reader transmitted RF signals [7]. In order to have a higher operating range, the minimization of energy consumption is extremely important when designing all aspects of the passive label circuit [8].

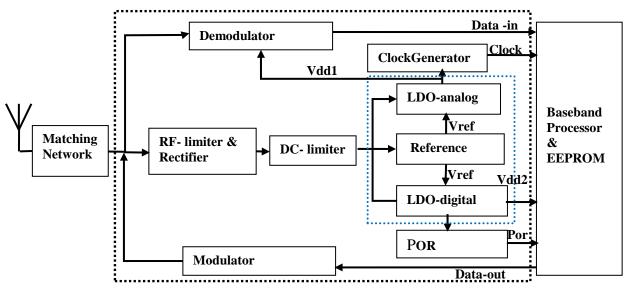

The figure 1 shows the building blocks for a passive RFID tag system. Therefore, the analog front-end operates in the following way: The rectifier converts the received RF electromagnetic wave into a DC signal. The output of the rectifier must be connected to a voltage regulator in order to obtain a stable voltage supply Vdd for the digital section and the analog front-end. Furthermore, the ASK demodulator (ASK: Amplitude Shift Keying) extracts out the data symbols (Data-in) which are embedded in the carrier waveforms. The backscatter modulation is obtained by switching the input impedance between two reflection states as dictated by the signal Data-out. The power-on-reset is responsible for generating the reset signal for the digital section and the clock generator generates the clock frequency for the digital section.

In this paper a high-performance analog front-end for the UHF passive RFID tag is proposed in compliance with the EPC C1 G2 standard [7]. The goal for the design of this tag is to maximize the read range while providing a full compliance with the protocol. The energy received by the tag depends on the reading distance. Indeed, if the reading distance is large then the energy received by the tag antenna decreases. The tag is entirely passive and relies on the energy provided by the incident radiation. It must receive sufficient energy to power all the tag circuits.

The analog front-end is one of the key elements in passive tags, including these diverse operations as the power generating circuit, the modulation circuit, the ASK demodulation circuit of the incident RF signal, the power on reset and the clock generator.

We are particularly interested by the power generation circuit which contains the matching circuit, the RF-limiter, the NMOS rectifier, the DC-limiter and the voltage regulation circuit. With the RF-limiter circuit and the NMOS rectifier has been already improved by another work that we published in

Fig.1. Block diagram of the Passive UHF RFID tag

[9] then the improved voltage regulation circuit will be the subject of this work.

In order to minimize consumption power for our system, we propose a reduction in the supply voltage of the analog circuits of 0.5V while maintaining a supply voltage to the digital part 1V. Thus, we will propose a voltage regulation system composed of two LDO regulators (LDO: Low Dropout) that share the same voltage reference. They are designed to generate two voltages. A voltage of 0.5 V noted Vdd1 which serves for the supply of the analog part and a voltage of 1V noted Vdd2 which serves for the supply of the digital part. To significantly reduce the energy consumption, we have designed the voltage reference and the amplifiers such a way that the transistors operate in the sub-threshold region.

The proposed system requires a minimum -24dBm input power with a  $50\Omega$  antenna at 900MHz.

A theoretical analysis and design techniques of the proposed power generating circuit, is presented in Section II. The clock generator is described in section III. In section IV, the design of the power -on-reset is presented. The ASK demodulator is addressed in section V.

The simulation results of the analog front-end proposed are presented in Section VI, followed by the conclusion in section VII. The technology used in this paper is 90 nm CMOS.

### II. POWER GENERATING CIRCUIT

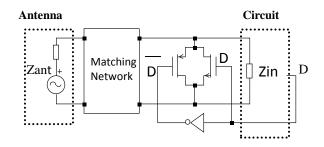

This circuit consists of the impedance matching circuit, the RF-limiter circuit, the NMOS Rectifier, the DC-Limiter and the proposed voltage regulation. The impedance matching circuit is required to ensure the maximum RF energy is transferred from the source to the load. The input impedance of a rectifier is generally much higher than the source impedance. The standard RF source impedance is considered

$50\Omega$ . The voltage sat the antenna of an RFID system can change from 300 mV to 20V, depending on the vicinity of the reader to the tag [10]. To prevent any damage to transistors at high voltage levels. The RF-limiter is used to ensure that under large RF power levels the voltage swing at the chip input is limited to a fixed value. The RF-limiter acts like a bypass system for the extra current during the large input power.

The NMOS rectifier is another work that we published in [9] converts a part of the RF signal power to DC for power supply for all active circuits on the chip. The efficiency of a rectifier decreases with an increasing number of rectifier stages [11]. Additionally, the working distance of RFID varies dramatically, so the dynamic range of RF input power may be as high as 30dB. In order to make all the circuits work normally, the power supply cannot be too high. The DC-limiter is another work that we published in [9] is needed to limit the power amplitude when the rectifier is in the near field.

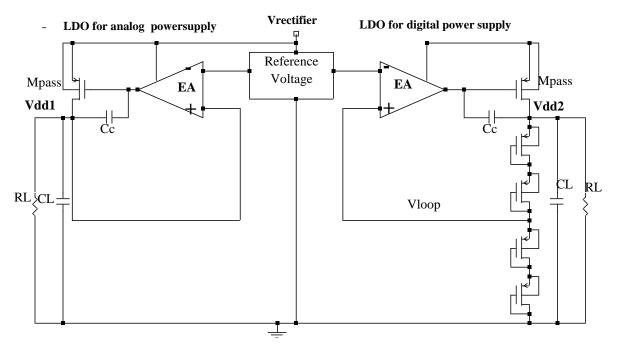

The output of the NMOS rectifier must be connected to a voltage regulator. The regulator has taken two main functions: Regulate the front-end output voltage to a preferred value and within a preferred range and protect the inner circuits from breaking at high RF input power. Moreover, RFID tags are usually placed in harsh environments; such that, the operation of a regulator also needs to operate over a wide range of temperature and supply voltage variations. From all the requirements, the series LDO voltage regulator is preferred to use as the regulator topology. Fig.2 shows the block diagram of the proposed voltage regulation. Another, to avoid the interference of the digital switching noise in to the sensitive analog supply voltage reference are designed to generate a

Fig.2. Diagram of the proposed voltage regulation

Vdd1 (0.5V) for the analog power supply and Vdd2 (1V) for the digital power supply respectively.

## C.1 Reference voltage generator

The figure 3 shows the schematic of the reference voltage generator, which is a variant of the generator proposed in [13],[14]. The latter composed by current source current source sub-circuit and bias voltage sub-circuit. The former generates a bias current ( $I_{GS}$ ), while the latter accepts IGS and produces the output voltage ( $V_{ref}$ ). Under a small supply voltage, most transistors will work in the subthreshold region. The characteristic equation of a transistor operating in the subthreshold region can be expressed as [13].

In this design, the reference voltage is 504mV for the supply voltage of 1.2V with line regulation of 0.9mV/V. The temperature ranges from  $-30^{\circ}\text{C}$  to  $50^{\circ}\text{C}$ , with the TC of  $12\text{ppm/}^{\circ}\text{C}$ .

## C.2 Series Voltage Regulator

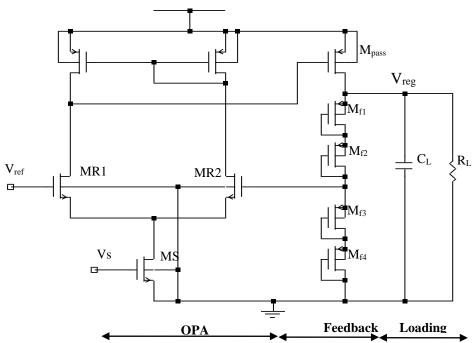

The schematic of LDO is shown in Fig. 3, where the OPA(error amplifier) compares the feedback signal from  $V_{reg}$  with  $V_{ref}$  before producing an error signal to drive the pass device  $M_{Pass}$  for the constant  $V_{reg}$ .

The feedback signal is generated by a voltage divider, which consists of four diode connected transistors  $(M_{f1} \sim M_{f4})$ . The stability of  $V_{reg}$  strongly depends on the bias current

$I_{SS}$  of the OPA, as shown in the following equation:

$$\frac{\Delta V_{reg}}{\Delta I_{SS}} \approx -\frac{(\frac{r_{on} \parallel r_{op}}{2})g_m p_{ass}(r_{oPass} \parallel R_L)}{1 + (\frac{r_{on} \parallel r_{op}}{2})g_m p_{ass}(r_{oPass} \parallel R_L)\frac{g_{mR}R_{f3,4}}{R_{f3,4} + R_{f1,2}}}{\approx -\frac{1}{g_{mR}}\frac{R_{f3,4} + R_{f1,2}}{R_{f3,4}}}$$

(1)

where  $r_{on}(r_{op})$  is the output resistance of NMOS (PMOS) transistor,  $r_{oPass}$  and  $R_L$  the output resistance of  $M_{Pass}$  and the load resistor,  $g_{mR}$  and  $g_m p_{ass}$  the transconductance of NMOS in the differential pair and  $M_{Pass}$ , and  $R_{f1,2}$  and  $R_{f3,4}$  are the equivalent resistance of  $M_{f1}$  to  $M_{f4}$ , respectively.

The regulated voltage variation caused by  $\Delta V_{DD}$  (line regulator) can be approximated as

$$\frac{\Delta V_{reg}}{\Delta V_{DD}} \approx -\frac{\frac{g_{mPass}r_{oPass}R_{L}}{r_{oPass} + R_{L}}}{\frac{g_{mR}(r_{on} \parallel r_{op})g_{mPass}(r_{oPass} \parallel R_{L})R_{f3,4}}{R_{f3,4} + R_{f1,2}}}$$

$$\approx \frac{1}{g_{mR}(r_{on} \parallel r_{op})} \frac{R_{f3,4} + R_{f1,2}}{R_{f3,4}}$$

(2)

Where  $g_{mR}(r_{on} || r_{op})$  represents the voltage gain of the differential amplifier. The effect of load current on the regulated voltage (load regulation) can be approximated as

$$\frac{\Delta V_{reg}}{\Delta I_L} \approx \frac{r_{o,Pass}}{1 + A_V P_2 F_B}$$

$$\approx \frac{r_{o,Pass}}{g_{mR}(r_{on} \parallel r_{op}) g_{mPass}(r_{oPass} \parallel R_L) \frac{R_{f3,4}}{R_{f3,4} + R_{f1,2}}$$

(3)

From (1) and (3), a high voltage gain of the amplifier with large channel length for transistors MR1 and MR2 will help improve both LIR and LOR. In addition, the output resistance of the pass device can be reduced by using short channel PMOS transistor.

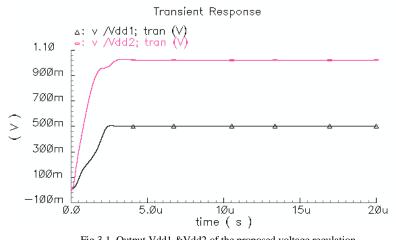

The proposed voltage regulator is implemented in 90 nm CMOS technology. The output voltage is 1.01 V with line regulation of 5.9 mV/V. The load regulation is estimated to be 76.21  $\mu$ V/49  $\mu$ A. The PSRR (power supply rejection ratio) for the regulated voltage is -65.4dB at 100Hz and -60.5dB at 1MHz. The temperature ranges from -30 °C to 50 °C, with the TC of 31.3 ppm/°C. The gain and the phase margin are 80.6 dB and 89.7° respectively, show that the voltage regulator is stable. Fig 3.1 shows the output Vdd1 &Vdd2 of the proposed voltage regulation.

Fig.3. The schematic of LDO regulator

Fig.3.1. Output Vdd1 &Vdd2 of the proposed voltage regulation

# III. CLOCK GENERATOR

The clock generator is needed for the digital section to run and to decode the data. Depending on the system, the clock can be either generated on chip or it can be extracted from the incoming carrier signal. For RFID technology for generating the internal clock there are different circuits that can be used such as current starved ring oscillators, relaxation oscillators, and phase locked loop (PLL), although the latter consumes too much power so it is normally not recommended for RFID.

The ring oscillators can have different amounts of stages, with the output of the last stage fed into the input of the first stage. They have the advantage of being able to operate without bulky passive components such as capacitors, resistors and inductors, making them the preferred topology

as they consume less power and take up less area, which are the most important factors when it comes to clock generators [15]. Today the electronic product- code Class-1 Generation-2 (EPC C1G2) standard [15] is a major UHF RFID standard which ensures reliable data rates and better performance of RFID applications. According to the EPC C1G2 protocol, a system clock of at least 1.28 MHz is needed for the tag.

[1

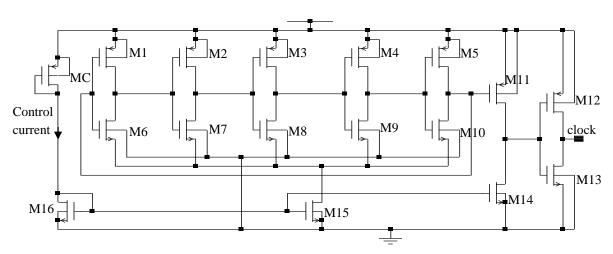

The ring oscillator proposed is shown in Fig.4. The control current tunes the oscillation frequency and the W/L ratio of the MOS transistors is dimensioned so that with the control current of 65.5 nA at a power supply of 0.5V.

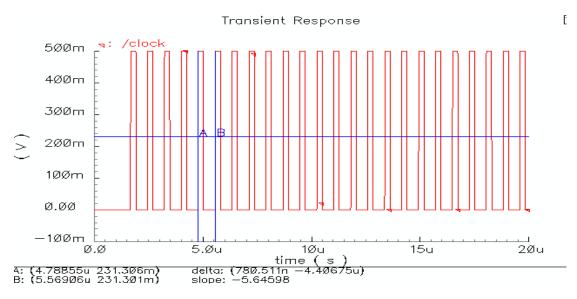

Table 1 shows the ring oscillator parameters and Fig.4.1 shows output of the oscillator has a nominal frequency of 1.28 MHz.

| TABLE I                        |            |                   |  |  |  |

|--------------------------------|------------|-------------------|--|--|--|

| THE RING OSCILLATOR PARAMETERS |            |                   |  |  |  |

|                                |            |                   |  |  |  |

| Oscillation Frequency          | Duty cycle | Power consumption |  |  |  |

| 1.28MHz                        | 30.86%     | 98nW              |  |  |  |

Fig.4. Schematic proposed of the ring oscillator

Fig. 4.1. Output of the ring oscillator

# IV. POWER-ON-RESET

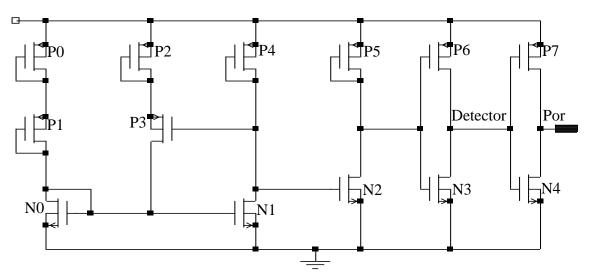

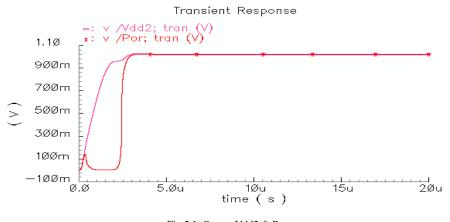

The power-on reset (POR) circuit, shows in Fig.5 is responsible for generating the reset signal for the digital section, as well as disconnecting the transponder to avoid malfunction once the required power falls below a certain level, fig.5.1 shows output Vdd2 & Por. Simply put, if the power supply voltage is lower than the reference voltage, the POR circuit has to release control of the baseband processor. If the power supply voltage level is higher than the reference voltage, the POR circuit has to generate the signals to reset and initiate operation of the digital synchronous baseband processor circuit [16].

Fig.5. The schematic of power-on reset

Fig.5.1. Output Vdd2 & Por

# V. ASK DEMODULATOR

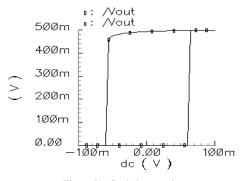

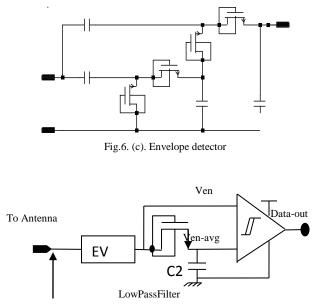

The block diagram of the demodulator part was shown in Fig. 6(d). The latter uses the envelope detection and comparison with the average of the input voltage to recover baseband data. The envelope detector, shows in Fig.6(c) is consists of a two-stage rectifier is transferred through a low pass filter to get its average value [17]. The envelope detector and its average value are then compared using a comparator with hysteresis. The comparator needs hysteresis for deal with the voltage ripple from the envelope detector.

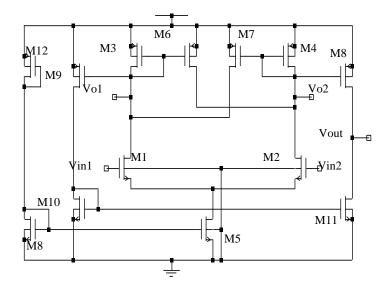

The main parameter of comparator with hysteresis is the trip point,  $V_{TRP}$ , which is the threshold that the input has to reach before the output changes. There are two trip points, one is positive trip point,  $V_{TRP}^+$ , which the input has to reach when it goes from negative to positive before the output changes, and the other is negative trip point,  $V_{TRP}^-$ , which the input has to reach when going from positive to negative. Fig. 6(a) shows a schematic of comparator with internal hysteresis. For Vin1 is on ground, the positive trip point is given by (4) when Vin2 goes from negative to positive as

$$V_{TRP}^{+} = V_{GS2} - V_{GS1} = \left(\frac{2i_2}{\beta_2}\right)^{1/2} + V_{T2} - \left[\left(\frac{2i_1}{\beta_1}\right)^{1/2} + V_{T1}\right] (4)$$

When Vin2 reaches the trip point, Vo1 and Vo2 change its voltage. At the switching point, we have the relation between currents in transistors [18] as

$$i_{1} = i_{3} = \frac{i_{5}}{1 + \left[ \left( W/L \right)_{6} / \left( W/L \right)_{3} \right]}, i_{2} = i_{5} - i_{1}(5)$$

And when Vin2 goes from positive to negative, the negative trip point  $V_{TRP}^{-}$  is given by

$$\bar{V_{TRP}} = -\left[\left(\frac{2i_2}{\beta_2}\right)^{1/2} + V_{T2} - \left[\left(\frac{2i_1}{\beta_1}\right)^{1/2} + V_{T1}\right]\right](6)$$

where  $\beta_{1,2}$  and  $V_{T1,2}$  are the transconductance and the threshold voltages of the transistors M1 and M2, respectively. Fig. 6(b) shows the simulation result of the designed comparator with Vdd1=0.5 V, Vin1=0V, V<sub>TRP</sub>= ±60 mv.

Fig.6. (a). Circuit schematic of comparator with internal hysteresis

Fig.6. (b). Cycle hysteresis

1

Fig.6. (d). Schematic of ASK demodulator

As a counter part of the demodulator, the return link modulator is another essential part of the RFID tag. By changing the tag IC's input impedance, the electromagnetic wave scattered back by the antenna is modulate [2].A passive RFID tag typically uses this mechanism for the return link. ASK backscatter modulation is used in our design. The schematic of the proposed modulator is shown in Fig.7. The switches in the backscattering circuit are realized using two minimum lengths NMOS and PMOS transistors with 1µm width in parallel to linearize the switch resistance in the large dynamic range of the input signal.

Fig.7. Schematic of the backscatter modulator

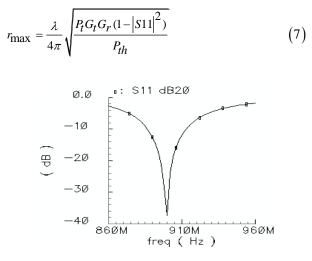

The input S11 reflection coefficient is shown as a function of frequency in Fig.8. The S11 at 900 MHz is around -38dB which illustrate a good matching at that frequency.

The communication range depends on the power reflection and can be calculated using the friis free space formula [15]:

Fig.8. The S11 as a function of frequency

### VI. SIMULATIONS RESULTS

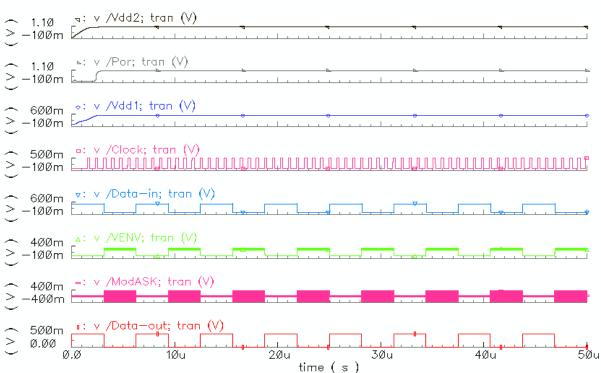

The simulation results of the main blocks of the analog front-end of the passive UHF RFID tag, is shown in Fig.9 (a), under conditions is 900 MHz, and the data rate is the 160 Kbit/s. The power consumption of the main blocks is shown in table 2. Table 3 compares the power consumption of this work to other reported work. The sensitivity of the analog front-end is -24 dBm to generate a Vdd1 (0.5 V) for the analog supply and Vdd2 (1 V) for digital power supply from a 50  $\Omega$  antenna at 900 MHz. The operating range of the RFID circuits is expressed in terms of wavelengths instead of frequency for more relevant comparisons.

A comparison among our RFID circuit and some previously reported works is summarized in table 4.

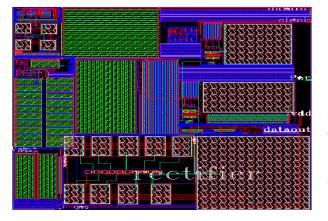

The Layout of proposed analog front-end is shown in Fig.9 (b). The size of whole chip is only 79  $\mu$ m × 83  $\mu$ m.

TABLE II POWER CONSUME OF MAIN BLOCKS

| Block   | power generating circuit & | Demodulator | Clock |

|---------|----------------------------|-------------|-------|

|         | Power-on-reset             |             |       |

| Power   | 476nW                      | 367nW       | 98nW  |

| Consume |                            |             |       |

TABLE III COMPARISON OF POWER CONSUMPTION

| Work                    | [2]    | [19]    | [20]    | This work |

|-------------------------|--------|---------|---------|-----------|

| Frequency (MHz)         | 900    | 900     | 900     | 900       |

| CMOS process            | 0.5 µm | 0.25 μm | 0.18 µm | 90 nm     |

| Power consumption (µ W) | 2.25µ  | 8μ      | 2.2μ    | 0.941 µ   |

| Ref.               | Efficiency | Minimum Input Power | Range             | Carrier Frequency | Process     |

|--------------------|------------|---------------------|-------------------|-------------------|-------------|

| This work          | 28%        | 4.2µW**             | 77.6λ***          | 900MHz            | 90 nm CMOS  |

| [9]                | 26.96%     | 5.01µW **,15.8 µW*  | 70.8 <i>\</i> *** | 900MHz            | 90 nm CMOS  |

| [2]Schottky Diodes | 14.5 %     | -                   | 28.2λ             | 900MHz            | 0.5 µm CMOS |

| [21]               | 10.94%     | 63µW *              | 21.32***          | 450MHz            | 0.25µm CMOS |

TABLE IV COMPARISON RESULTS

\* Normalized for 3V generation, \*\*Normalized for 1V generation, \*\*\* Normalized for 4W EIRP source

Transient Response

Fig.9.(a). Simulation results of the whole main blocks of the analog front-end

Fig.9.(b).Layout of proposed analog front-end

# VII. CONCLUSION

This paper presented a high-performance analog front end for passive UHF RFID tag, which is designed by using the 90 nm CMOS process, consisting of a power generating circuit which consists of the matching & the RF-limiter, the NMOS rectifier, the DC-limiter and the proposed voltage regulation. The modulation and demodulation, power-on-reset, clock generator. The whole analog front-end circuit consumes only 941nW and works in low voltage, 1V. The simulations have been done to verify the proposed ideas.

1

## REFERENCES

- Nakamoto H, Yamazaki D, Yamamoto T, et al. A passive UHF RF identification CMOS tag IC using ferroelectric RAM in 0.35um technology. IEEE J Solid-State Circuits, 42(1), 101,2007.

- [2] Karthaus U, Fischer M. A Fully integrated passive UHF RFID transponder IC with 16.7 μW minimum RF input power. IEEE J Solid-State Circuits, 38(10),1602,2003

- [3] Barnett R E, Liu J, Lazar S.A RF to DC voltage conversion model for multi-stage rectifiers in UHF RFID transponders. IEEE J Solid-State Circuits, 44(2),354,2009.

- [4] G .De Vita, & G. Iannaccone. Ultra-low power RF section of a passive microwave RFID transponder in 0.35 μm BiCMOS. Circuits and Systems. ISCAS 2005. IEEE International Symposium on. IEEE, 2005.

- [5] T.Umeda, H. Yoshida, S. Sekine, Y. Fujita, T. Suzuki, and S. Otaka. A 950- MHz Recifier Circuit for Sensor Network Tags with 10-m Distance. IEEE Journal of Solid-State Circuits, 41(1), 35-41, 2006.

- [6] Z. Liu, C. Zhang, Y. Li, Z. Wang, Z. Wang A Novel Demodulator for Low Modulation Index RF Signal in Passive UHF RFID Tag. IEEE International Symposium on Circuits and Systems, 2109-2112, 2009.

- [7] J. Guo, W. Shi, K. Leung, and C. Choy. Power-On-Reset Circuit with Power-Off Auto-Discharging Path for Passive RFID Tag ICs. IEEE International Midwest Symposium on Circuits and Systems, pp. 21-24, August 2010.

- [8] G. De Vita & G. Iannaccone .Design criteria for the RF section of UHF and microwave passive RFID transponders. IEEE Transactions on Microwave Theory and Techniques. 53(9), 2978-2990, 2005.

- [9] Smail Hassouni, Hassan Qjidaa. A design of analog VDD generator for passive UHF RFID Tag in 90 nm CMOS. International Journal of Microwave and Wireless Technologies. 7(5), 507–513, 2015. Cambridge Press DOI 10.1017/S175907871 4000841

- [10] D.K. Cheng, Field and Wave Electromagnetics. Reading, MA: Addison Wesley, 1989D. M. Dobkin, The RF in RFID: passive UHF RFID in practice, 1st ed., Newnes, Oct. 2007.

- [11] J.W.Lee, D. H.T.Vo, Q.H.Huynh, S.H.Hong, A fully integrated HF-band passive RFID tag IC using 0.18 μm CMOS technology for low cost security applications, IEEE Trans. Ind. Electron. 58(6),2531–2540,2011.

- [12] K. Ueno, T. Jirose, T. Asai, and Y. Amemiya. A 300nW, 15ppm/°C, 20ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs. Solid-State Circuits, IEEE Journal of, vol. 44, no. 7, pp. 2047-2054, July. 2009.

- [13] J. Jeidrich, D. Brenk, J. Essel, M. Heinrich, M. Jung, G. Hofer, G. Holeg, R. Weigel, and G. Fischer. Design of a Low-Power Voltage Regulator for RFID Applications. Computational Technologies in Electrical and Electronics Engineering (SIBIRCON), 2010 IEEE Region 8 International Conference on, pp. 552-557, July. 2010.

- [14] M.-L. Hsia, Y.-S. Tsai, and O. Chen. An UHF Passive RFID Transponder Using A Low-Power Clock Generator without Passive Components. IEEE International Midwest Symposium on Circuits and Systems, vol. 2, pp. 11-15, August 2006.

- [15] EPCTM Radio-Frequency Identity Protocols Class-1 Generation-2 UHF RFID Protocol for Communications at 860 MHz – 960 MHz Version 1.2.0., 2008.

- [16] P. E. Allen, D. R. Holberg. CMOS analog circuit design. Oxford Univ. Press 2002.

- [17] Smail Hassouni, Hassan Qjidaa. A Design of Modulator and Demodulator for a Passive UHF RFID Tag Using DTMOST compatible with C1 G2 EPC standard protocol. International Journal of Wireless Information Networks. Volume 22, Issue 4 (2015), pp 407-414, Springer. DOI 10.1007/s10776-015-0292-x.

- [18] N.Cho, S. J. Song, J. Y. Lee, S. Kim, H. J. Yoo. A 8-μW, 0.3-mm 2 RFpowered transponder with temperature sensor for wireless environmental monitoring. In Circuits and Systems. ISCAS 2005. IEEE International Symposium on (pp. 4763-4766). 2005.

- [19] S. Zhang, L. Sun, H. Hong, J. Liu, J. Han, &S.Luo. A low-power analog front end of passive UHF RFID tag IC for EPC<sup>TM</sup> C1G2. In ASIC, 2009. ASICON'09. IEEE 8th International Conference on pp. 557-560.

- [20] F. Kocer and M.P. Flynn. A New Transponder Architecture with on-chip ADC for Long-Range Telemetry Applications. IEEE Journal of Solid-State Circuits, Vol. 41, pp. 1142-1148, 2006.

[21] P. V. Nikitin et al., "Power Reflection Coefficient Analysis for Complex Impedances in RFID Tag Design" IEEE Trans. On Microwave Theory and Technology, vol. 53, no. 9, pp. 2721-2725, Sept. 2005.

Smail Hassouni received the B.Sc. and MSc. degrees in engineering science from the Faculty of science, University of Sidi Mohammed Ben Abdellah, Fez, Morocco in 2009 and 2011, respectively, and the Ph.D. degree in electrical engineering from the Faculty of science, University of Sidi Mohammed Ben Abdellah, Fez, Morocco in 2016. His interests are low-power circuit design techniques for RFID, RF front-ends for passive tags, CMOS mixed-mode integrated

circuit design.

Hassan Qjidaa received the M.S. and Ph.D. degrees in electrical engineering from Nuclear Physics Institute of Lyon, in France 1984 and 1987, respectively. Since 1987, he served as a Research Scientist at Faculty of science in the University of Sidi Mohammed Ben Abdellah, Fez, Morocco. He has been a Professor with the Department of Physics. He is currently also a Director of the Information Analysis and Micro-system Teams (IAMS), and Vice Director of the electronic signal

and systems laboratory (LESSI). He is current research interests are in image processing, pattern recognition, data analysis, machine intelligence, low-power circuit design techniques for RFID, RF front-ends for passive tags, CMOS mixed-mode integrated circuit design and Artificial Intelligence.