# A Novel Approach to Design 2-bit Binary Arithmetic Logic Unit (ALU) Circuit Using Optimized 8:1 Multiplexer with Reversible logic

Vandana Shukla, O. P. Singh, G. R. Mishra, and R. K. Tiwari

Abstract— Reversible circuit designing is the area where researchers are focussing more and more for the generation of low loss digital system designs. Researchers are using the concept of Reversible Logic in many areas such as Nanotechnology, low loss computing, optical computing, low power CMOS design etc. Here we have proposed a novel design approach for a 2-bit binary Arithmetic Logic Unit (ALU) using optimized 8:1 multiplexer circuit with reversible logic concept [1]. This ALU circuit can perform complement, transfer, addition, subtraction, multiplication, OR, XOR, NAND functions on given values. The ALU circuit has been simulated on Modelsim tool and synthesised for Xilinx Spartan 3E with Device XC3S500E with 200 MHz frequency. This 2-bit ALU using reversible logic is useful for the designs of low power loss systems.

Keywords— Reversible circuit design, 2's Complement, Comparator, Adder, Subtractor, Multiplier, Reversible gates, Multiplexer circuit

#### I. INTRODUCTION

Arithmetic Logic Unit (ALU) is a vital component of any computing system. It is a digital circuit that performs the required arithmetic as well as logical operations on the operands. Earlier Von Neumann proposed first ALU in 1945 when he was working on EDVAC [2]. Conventionally ALUs were designed using basic logic gates such as AND, OR, NOT etc. However these gates dissipate some amount of energy due to the information loss during the operation. The amount of energy loss for one bit of information loss was calculated as kTln2 joules by R. Landauer in 1961 [3]. In 1965 G. E. Moore has given his famous Moore's law in which he stated that the number of transistors incorporated on a unit chip area doubles in an approximate time span of two years [4]. As a result of increase in the component density the amount of heat loss increases exponentially. In 1973 C. H. Bennette has shown that this amount of heat generation or energy loss can be minimized or removed (ideally) from the system by redesigning the same digital circuit using reversible logic gates [5].

Manuscript received February 5, 2015; revised June 11, 2015.

V. Shukla, O. P. Singh, and G. R. Mishra are with the Amity School of Engineering & Technology, Amity University Uttar Pradesh Lucknow Campus, India. (E-mails: vandanashuklaec05@gmail.com, opsingh@amity.edu, gr\_mishra@rediffmail.com).

R. K. Tiwari is with the Department of Physics and Electronics, Dr. R. M. L. Avadh University Faizabad, India. (E-mail: rktiwari2323@yahoo.co.in).

Earlier Lekshmi Viswanath et al proposed a reversible ALU circuit in 2012 which perform three arithmetic and five logical operations [6]. After that, in the same year Akansha Dixit et al proposed a new approach to design ALU circuit using reversible logic which perform increment, decrement, addition, subtraction, OR, XOR, AND, transfer and complement operations [7]. Later in 2014 S. Anusha et al has given a novel approach to design the ALU circuit with reversible logic using Arithmetic, logic, shift and multiplier circuit block [8].

This paper is organized in six sections to provide the clear view of the proposed ALU circuit. Section I and II provide the introduction of the research work and fundamental concepts of reversible logic concept respectively. After that section III and IV provide the knowledge about the concept of 2-bit ALU circuit and proposed approach to design 2-bit ALU using reversible logic respectively. Result and analysis of the proposed design approach is provided in the section V and conclusion of the paper with future scope is elaborated in the section VI at the end.

#### II. REVERSIBLE LOGIC FUNDAMENTALS

The fundamental concepts of Reversible logic are described in following subsections in brief:

#### A. REVERSIBLE LOGIC GATES

Reversible logic gates are described as (n, n) digital gates where n, n represents equality of number of input and output signals [9-11]. Any reversible logic gate must have following features:

- [1] Equal number of bits in input and output.

- [2] One to one mapping between input and output bits.

- [3] Fan-out of each gate must be equal to one.

In reversible logic gates, we can generate the applied input combination by knowing the output status at any instance. Above features discriminate these gates from the existing conventional (irreversible) logic gates.

### B. EXAMPLES OF REVERSIBLE LOGIC GATES

Researchers have proposed various reversible logic gates. Some of which are illustrated in table 1 in the form of block diagram, size and output equations etc.

| S.<br>No | Name of<br>Reversible<br>Logic Gate | Size<br>of<br>the<br>Gate | Block Diagram                    | Output Equations                                                                                                                                          |  |  |  |

|----------|-------------------------------------|---------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1        | Feynman<br>Gate [12]                | 2×2                       | A - P Feynam Gate  - Q           | $P = A;$ $Q = A \bigoplus B;$                                                                                                                             |  |  |  |

| 2        | TKS Gate [13]                       | 3×3                       | A — P  B — TKS Gate — Q  C — R   | $P = A.C' + B.C;$ $Q = A \bigoplus B \bigoplus C;$ $R = A.C + B.C';$                                                                                      |  |  |  |

| 3        | Peres Gate [14]                     | 3×3                       | A — P  B — Peres Gate — Q  C — R | P = A;<br>$Q = A \bigoplus B;$<br>$R = A.B \bigoplus C;$                                                                                                  |  |  |  |

| 4        | TR Gate<br>[15]                     | 3×3                       | A — P B — TR Gate — Q C — R      | P = A;<br>$Q = A \bigoplus B;$<br>$R = A.B' \bigoplus C;$                                                                                                 |  |  |  |

| 5        | Toffoli<br>Gate [16]                | 3×3                       | A — P  Toffoli Gate — Q  C — R   | $P = A;$ $Q = B;$ $R = A.B \bigoplus C;$                                                                                                                  |  |  |  |

| 6        | URG Gate<br>[10]                    | 3×3                       | A — P B — URG Gate — Q C — R     | $P = (A+B) \bigoplus C;$<br>Q = B;<br>$R = A.B \bigoplus C;$                                                                                              |  |  |  |

| 7        | VSMT<br>Gate [17]                   | 6×6                       | A P P P Q C VSMT R Gate F T T U  | $P = E'.(A.F'+B.F)+$ $E.(C.F'+D.F);$ $Q = A \bigoplus B \bigoplus C;$ $R = E \bigoplus F;$ $S = C \bigoplus D;$ $T = D \bigoplus E \bigoplus F;$ $U = E;$ |  |  |  |

TABLE I EXAMPLES OF SOME REVERSIBLE LOGIC GATES

#### C. CONSTANT INPUT SIGNALS

These are additional signals required at the input stages of reversible logic gates to complete the designed circuit using reversible logic approach. These constant input signals may be either high or low according to the requirement of the desired working of the designed circuit.

# D. GARBAGE OUTPUT SIGNALS

These signals are defined as those unwanted additional signals generated from the designed reversible circuit to complete the working of the circuit according to the requirement of the target system. These signals are equivalent to the bit loss in the irreversible gates as garbage signals are unused output signals.

#### E. OUANTUM COST

Quantum cost of any reversible logic gate or circuit is defined as the required number of  $1\times1$  or  $2\times2$  basic reversible gates to

design the same. The quantum cost of  $1\times1$  reversible gate is zero and that of  $2\times2$  reversible gate is 1. So the overall cost of reversible gate or circuit can be calculated based on the required number of these basic reversible gates.

#### F. REVERSIBLE CIRCUIT DESIGN

This concept aims to replace the design entities of the target digital circuit with reversible logic gates to design the same with reversible approach [18-21]. The designed reversible circuit must have following features:

- [1] Use of minimum number of reversible gates to design the target circuit.

- [2] Generation of minimum (ideally null) number of garbage output signals from the designed reversible circuit.

- [3] Requirement of minimum (ideally zero) number of constant input signals.

- [4] Minimum total quantum cost of the circuit.

- [5] No feedback connection in the designed reversible circuit.

# III. TWO-BIT ARITHMETIC LOGIC UNIT FUNDAMENTALS

Arithmetic logic unit is a vital component of any computing system. It performs all the necessary arithmetical as well as logical operations on the data to provide the required output. Here we are planning to design a small ALU circuit which performs some arithmetical as well as some logical operations on the two bit binary operand. Following components are required to design this proposed ALU circuit:

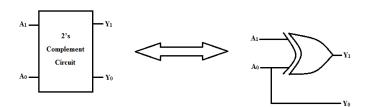

## A. Complement Circuit

This circuit provides the 2's complement of the entered two bit binary input number. Figure 1 shows the complement circuit using conventional basic logic gates and corresponding block diagram of the complement circuit.

Fig 1: Block diagram and logic implementation of Complement Circuit using conventional approach

Here output equations are as follows:

$$\mathbf{Y}_1 = \mathbf{A}_1 \bigoplus \mathbf{A}_0;$$

$$Y_0 = A_0;$$

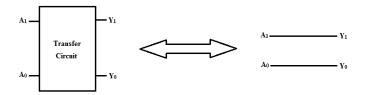

## B. Transfer Circuit

This circuit transfers the applied signals to the output side after some time delay only. Figure 2 below shows the block diagram as well as conventional circuit of transfer circuit of proposed ALU for 2-bit binary numbers.

Fig 2: Block diagram and logic implementation of Transfer Circuit using conventional approach

Where  $Y_1 = A_1$  and  $Y_0 = A_0$  respectively.

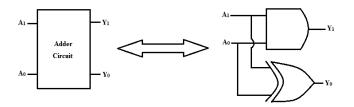

#### C. Adder Circuit

This circuit adds the applied bits of the binary number and provide the sum and carry bits of the result. Figure 3 below shows the block diagram and conventional digital circuit for this adder part of the proposed ALU circuit.

Fig 3: Block diagram and logic implementation of Adder Circuit using conventional approach

Where output bits are illustrated as follows:

$$Y_1 = Carry = A_1.A_0$$

;

$Y_0 = Sum = A_1 \bigoplus A_0$ ;

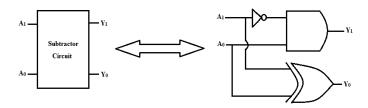

# D. Subtractor Circuit

This circuit subtracts the LSB  $(A_0)$  from MSB  $(A_1)$  of the applied binary number to provide the difference between the applied bits. The design of subtractor circuit using conventional approach is illustrated in figure 4.

Fig 4: Block diagram and logic implementation of Subtractor Circuit using conventional approach

Where output bits are calculated as follows:

$Y_1 = Borrow = A_1'.A_0;$

$\mathbf{Y}_0 = \mathbf{Sum} = \mathbf{A}_1 \bigoplus \mathbf{A}_0;$

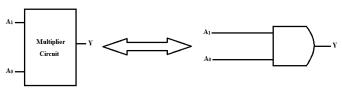

# E. Multiplier Circuit

This part of the ALU multiplies the applied bits of the binary number and provide the required multiplication result. We have shown the block diagram and design of this multiplier circuit using conventional irreversible gates in figure 5.

Fig 5: Block diagram and logic implementation of Multiplier circuit using conventional approach

The multiplier circuit shown in the above figure provide a single output which is  $Y (=A_1.A_0)$ .

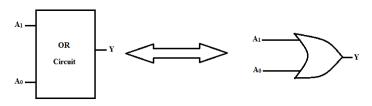

#### F. OR Circuit

The OR circuit performs the logical OR operation on the applied bits of the input signal. The conventional approach and block diagram of logical OR circuit is illustrated in figure 6.

Fig 6: Block diagram and logic implementation of OR Circuit using conventional approach

Here output equation is  $Y = A_1 + A_0$ .

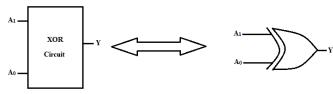

#### G. XOR Circuit

This part of the proposed ALU circuit performs the logical exclusive OR operation on the applied input bits. Figure 7 shows the block diagram and logical implementation of XOR circuit part of the proposed ALU circuit.

Fig 7: Block diagram and logic implementation of XOR Circuit using conventional approach

Output of XOR circuit is given as  $Y = A_1 \oplus A_0$ .

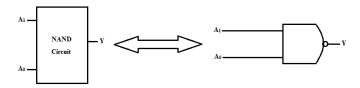

#### H. NAND Circuit

This circuit performs the logical NAND operation on the bits of the applied input signal. Figure 8 shows the block diagram as well as conventional design of this logical part of the target ALU circuit.

Fig 8: Block diagram and logic implementation of NAND Circuit using conventional approach

The output signal is shown in the following equation:  $Y = (A_1.A_0)$ ;

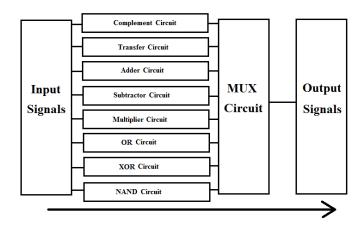

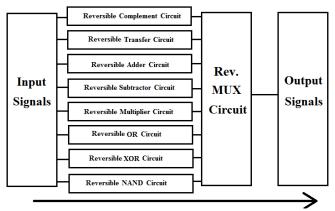

Above operational sub-parts of the proposed Arithmetic Logic Unit circuit are multiplexed using 8:1 multiplexer for appropriate integration. Figure 9 provides the block diagram of proposed designed Arithmetic Logic Unit.

Fig 9: Block diagram of 2-bit Arithmetic Logic Unit Circuit

This ALU performs some arithmetic (addition, subtraction, multiplication etc) as well as some logical (OR, XOR, NAND etc) operations on the applied 2-bit binary signals. Function table for this ALU circuit is demonstrated in table 2 below.

TABLE II FUNCTION TABLE OF 2-BIT BINARY ALU

| S.No.  | Selection Lines |       |       | Function Performed       |  |

|--------|-----------------|-------|-------|--------------------------|--|

| 5.110. | $S_2$           | $S_1$ | $S_0$ | Function Performed       |  |

| 1      | 0               | 0     | 0     | 2's Complement           |  |

| 2      | 0               | 0     | 1     | Transfer Operation       |  |

| 3      | 0               | 1     | 0     | Addition Operation       |  |

| 4      | 0               | 1     | 1     | Subtraction Operation    |  |

| 5      | 1               | 0     | 0     | Multiplication Operation |  |

| 6      | 1               | 0     | 1     | OR Operation             |  |

| 7      | 1               | 1     | 0     | XOR Operation            |  |

| 8      | 1               | 1     | 1     | NAND Operation           |  |

| 7      | 1 1             | 1 1   | 0     | XOR Operation            |  |

# IV. PROPOSED 2-BIT ALU CIRCUIT USING REVERSIBLE LOGIC

Arithmetic Logic Unit (ALU) circuit shown in figure 9 is designed using conventional irreversible gates such as AND, OR, XOR gates etc. These gates generate information loss which further enhances the amount of heat generation from the circuit. So here we propose the design of the same 2-bit ALU circuit using reversible logic concept by changing the design entities with reversible logic gates. Following subsections

provide the description of the design of required sub-circuits of the target ALU.

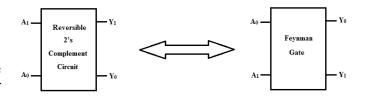

#### A. Reversible Complement Circuit

In figure 10 the reversible 2's complement circuit is designed using one Feynman gate for 2-bit binary number [12].

Fig 10: Block diagram and logic implementation of Reversible Complement Circuit

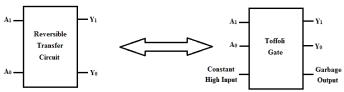

#### B. Reversible Transfer Circuit

Here only one Toffoli gate is required to transfer the applied 2- bit binary number to the output as illustrated in the figure 11 [16].

Fig 11: Block diagram and logic implementation of Reversible Transfer Circuit

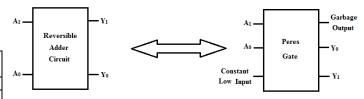

#### C. Reversible Adder Circuit

This sub-part of the 2-bit ALU circuit is designed with the help of single Peres gate as shown in figure 12 [14].

Fig 12: Block diagram and logic implementation of Reversible Adder Circuit

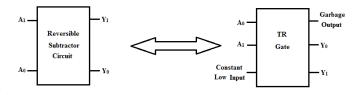

#### D. Reversible Subtractor Circuit

This reversible part of the aimed ALU circuit is designed using a single TR gate as shown in the figure 13 [15].

Fig 13: Block diagram and logic implementation of Reversible Subtractor Circuit

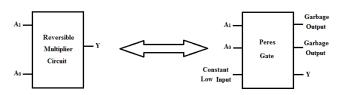

#### E. Reversible Multiplier Circuit

The two bit binary multiplier circuit with reversible logic concept is designed using single Toffoli gate as shown in figure 14 [16].

Fig 14: Block diagram and logic implementation of Reversible Multiplier Circuit

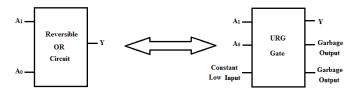

#### F. Reversible OR Circuit

The logical OR operation using reversible logic on the applied bits are implemented with the use of a single reversible logic URG gate as shown in figure 15 [10].

Fig 15: Block diagram and logic implementation of Reversible OR Circuit

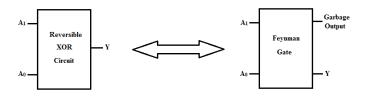

# G. Reversible XOR Circuit

This logical exclusive OR circuit using reversible logic is designed with the help of a single Feynman gate as shown in figure 16 [12].

Fig 16: Block diagram and logic implementation of Reversible XOR Circuit

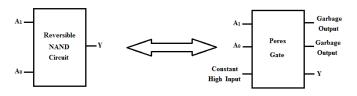

#### H. Reversible NAND Circuit

This part of the proposed ALU to perform logical NAND operation on the bits of the applied input signal with reversible logic concept is implemented using a single Peres gate as shown in figure 17 [14].

Fig 17: Block diagram and logic implementation of Reversible NAND Circuit

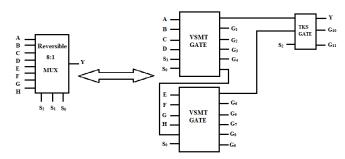

The 2-bit binary ALU circuits are designed through various reversible logic gates and integrated using 8:1 multiplexer. This optimized 8:1 multiplexer circuit uses two VSMT gate and one TKS gate as shown in the figure 18 [1,13,17].

Fig 18: Block diagram of optimized 8:1 multiplexer circuit using reversible logic

Here  $G_1$  to  $G_{11}$  are garbage output signals generated from the reversible circuit.

# Proposed 2-bit Binary ALU Using Reversible Logic

The previous circuits are used in the designing of ALU by integration connections shown in figure 19.

Fig 19: Block diagram of proposed 2-bit binary ALU circuit using reversible logic

The proposed ALU circuit using reversible logic conforms to the function table shown in table 2.

# V. RESULT AND ANALYSIS

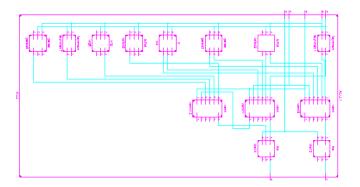

The proposed two bit arithmetic logic unit is simulated on Modelsim tool and synthesised for Xilinx Spartan 3E with Device XC3S500E with 200 MHz frequency. The simulation result of the proposed reversible logic based circuits are shown in figure 20.

Fig 20: Simulated waveform of proposed 2-bit binary ALU circuits using Reversible Logic

In figure 20 the output of the proposed reversible circuit follows table 2. The synthesized circuit for proposed ALU using reversible gate is shown in Figure 21.

Fig 21: Synthesized circuit of proposed 2-bit binary ALU circuit using Reversible Logic

#### VI. CONCLUSION AND FUTURE SCOPE

We have proposed a novel design of 2-bit binary Arithmetic Logic Unit (ALU) circuit using reversible logic. The proposed ALU can perform some arithmetical and some logical operations utilizing the optimized 8:1 multiplexer circuit using reversible logic. The proposed ALU circuit can be further explored and employed to design and implement various other low power loss applications and help the researchers to design better devices/systems.

# ACKNOWLEDGMENT

The authors are thankful to Mr. Aseem Chauhan (Additional President RBEF, Chancellor AUR), Maj. General K. K. Ohri, AVSM (Retd.), Pro Vice Chancellor, AUUP, Lucknow Campus, Wing Cd (Dr) Anil Kumar Tiwari (Director ASET), and Brig. Umesh K. Chopra (Director, AIIT, & Coordinator, ASET) for their cooperation, motivation and suggestive guidance.

#### REFERENCES

- [1] Vandana Shukla, O P Singh, G R Mishra, R K Tiwari, "AN OPTIMIZED CIRCUIT OF 8:1 MULTIPLEXER CIRCUIT USING REVERSIBLE LOGIC GATES", International Conference on Communication, Computing and Information Technology (ICCCMIT), 12-13 December 2014.

- [2] John Von Neumann, "First Draft of a Report on the EDVAC", University of Pennsylvania Moore School Library, June 30, 1945.

- [3] R. Landauer, "Irreversibility and Heat Generation in the Computational Process", IBM Journal of Research and Development, 5, pp. 183- 191, 1961.

- [4] G. E. Moore, "Cramming more compounds onto integrated circuits", Electronics, Vol. 38, No. 8, April 19, 1965.

- [5] C. H. Bennett, "Logical Reversibility of Computation", IBM J. Research and Development, pp. 525-532, November 1973.

- [6] Lekshmi Viswanath, Ponni. M, "Design and Analysis of 16 Bit Reversible ALU", IOSR Journal of Computer Engineering (IOSRJE), Vol. 1, Issue 1, pp. 46-53, May-June 2012.

- [7] Akansha Dixit, Vinod Kapse, "Arithmetic & Logic Unit (ALU) Design using Reversible Control Unit", International Journal of Engineering and Innovative Technology (IJEIT), Vol. 1, Issue 6, pp. 55-60, June 2012.

- [8] S. Anusha, M. Manoher Rao, N, Swetha Reddy, "Design, Analysis, Implementation and Synthesis of 16 Bit Reversible ALU by using Xilinx

- 12.2", International Journal of Engineering Research and Application (IJERA), Vol. 4, Issue 4, pp. 86-91, April 2014.

- [9] E. Fredkin and T. Toffoli, "Conservative Logic", Int'l J. Theoretical Physics, Vol. 21, pp. 219-253, 1982.

- [10] P. Kemtopf, "Synthesis of Multipurpose Reversible Logic Gates", Euromicro Symposium on Digital System Design (DSD'02), pp. 259-267, 2002.

- [11] B. Raghu kanth, B. Murali Krishna, M. Sridhar, V. G. Santhi Swaroop, "A Distinguish between Reversible and Conventional Logic Gates", International Journal of Engineering Research and Applications (IJERA), Vol. 2, Issue 2, pp. 148-151, Mar-Apr 2012.

- [12] R. Feynman, "Quantum Mechanical Computers", Optics News, Vol. 11, pp. 11-20, 1985.

- [13] H. Thapliyal, M. B. Srinivas, "Novel Design and Reversible Logic Synthesis of Multiplexer Based Full Adder and Multipliers", IEEE, Vol. 2, pp.1593-1596.

- [14] Peres, "Rversible Logic and Quantum Computers", Physical review A, 32:3266-3276, 1985.

- [15] H. G. Rangaraju, U. Venugopal, K. N. Muralidhara, K. B. Raja, "Low Power Reversible Parallel Binary Adder/Subtractor", International Journal of VLSI design and communication systems (VLSICS), Vol. 1, No. 3, Sept 2010.

- [16] T. Toffoli, "Reversible Computing", Tech memo MIT/LCS/ TM-151, MIT Lab for Computer Science, 1980.

- [17] Vandana Shukla, O. P. Singh, G. R. Mishra, R. K. Tiwari, "Novel Design of A Multiplexer Circuit Using Reversible Logic", IJCER, Vol. 3, Issue 10, pp. 30-35, Oct 2013.

- [18] A. N. Nagamani, H. V. Jayashree, H. R. Bhagyalakshmi, "Novel Low Power Comparator Design using Reversible Logic gates", Indian Journal of Computer Science and Engineering ( IJCSE ), Vol. 2, No. 4 Aug-Sept 2011.

- [19] M.P. Frank, "Introduction to Reversible Computing: Motivation, Progress and Challenges", Proceedings of the 2nd Conference on Computing Frontiers, pp. 385–390, 2005.

- [20] H. Thapliyal and N. Ranganathan, "Design of Reversible Sequential Circuits Optimizing Quantum Cost, Delay and Garbage Outputs," ACM Journal of Emerging Technologies in Computing Systems, Vol. 6, No. 4, pp. 14:1–14:35, Dec. 2010.

- [21] D. P. Vasudevan, P.K. Lala , J. Di and J.P Parkerson, "Reversible–Logic Design with Online Testability", IEEE Trans. on Intrumentation and Measurement, Vol. 55, No. 2, pp. 406 -414, April 2006.

- [22] H. G. Rangaraju, U. Venugopal, K. N. Muralidhara, K. B. Raja, "Low Power Reversible Parallel Binary Adder/Subtractor", International Journal of VLSI design and communication systems (VLSICS), Vol. 1, No. 3, Sept 2010.

Vandana Shukla is pursuing her Ph.D. in Engineering from Amity University. Presently working as faculty member in Department of Computer Science & Engineering Amity School in of Technology, Engineering & Amity University Uttar Pradesh Campus. She is also a member of Institution of Electronics Telecommunication Engineers (IETE) and

the Institution of Engineering & Technology (IET-UK). She has presented several papers in various National and International Conferences and also published papers in National/international Journals. Her area of interest includes Digital Circuit Design and Computer Organization & Architecture.

O. P. Singh has completed his Ph.D. degree from IIT BHU. He had a work experience of sixteen years in teaching. Presently he is head of department of electrical and electronics in Amity School of Engineering & Technology, Amity University Uttar Pradesh Lucknow Campus. He is also a member of Indian society of remote sensing (ISRS), the Institution of Engineering & Technology (IET-UK) and

Material Research Society of India (MRSI). His area of research include digital electronics engineering, microwave and antenna design, control system, pattern recognition in image compression etc.

G. R. Mishra obtained his Ph. D. in Electronics from Avadh University. He has over fourteen years experience and presently working as faculty members in Department of Electronics & Communication Engineering, Amity School of Engineering & Technology, Amity University Uttar Pradesh Lucknow Campus. He is life member of Institution of Electronics & Telecommunication Engineers (IETE), the Institution of

Engineering & Technology (IET-UK) and Material Research Society of India (MRSI). He has presented several papers in National Seminar/Conferences and also published papers in National/international Journals. His area of interest includes Digital System Design, Microprocessor Based System Design, Signal Processing, Embedded Systems and VLSI Design.

R. K. Tiwari received M.Sc Degree in Physics specialization in Electronics from Allahabad University and obtained Gold Medal .He received Ph. D degree in Physics from Dr. R. M. L. Avadh University Faizabad. He has been working as a faculty in various capacity and Ex-Head department of Physics and Electronics and presently working as director I. E. T. Dr. R. M. L. Avadh University Faizabad. He has 29 years of rich teaching experience at U.G and P.G

level. He has produced 12 Ph.D students and has published more than 65 papers in various national and international journal. He has received various fellowship award as NET, CSIR (JRF and SRF) and Wardvedant Gold Medal, Allahabad University. He is life member of Vigyan Parisad Prayag, founder member of IAPS Allahabad and Board of Governers, Dr. R. M. L Avadh University Faizabad.